Also mit Leiterbahnen, Spannungswandlern, Bauteileplatzierung etc. und natürlich Details warum es so gemacht wurde und am besten noch eine Entwicklungschronik dazu

Das ist oft überraschend einfach wenn man das Platinenlayout vor Augen hat. Bei Datenleitungen, etwa Leitungen mit differentiellen Adernpaaren wechseln sich diese ab, dazwischen kommt eventuell eine Masseleitung zur Schirmung. Abzweigungen und Kurven werden als rechte Winkel ausgeführt. Das ermöglicht die beste Signalqualität.

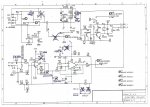

Die Spannungsversorgung ist wesentlich komplizierter. Da Hochleistungs-ASICs wie CPUs oder GPUs oft enorm hohe Ströme (bis über 100A) bei recht niedrigen Spannungen benötigen und die Ströme zudem im kHz Bereich erheblich schwanken können. Dennoch muss gewährleistet sein das einerseits die Spannung stabil bleibt und andererseits die SpaWas und die Platine nicht abbrennen. Allerdings, das muss man auch sagen gibt es oft Referenzlösungen für die Spannungsversorgung die etwa von Intel entwickelt und dann von vielen MB Herstellern übernommen werden. Diese Referenzimplementierungen werden zum Teil auch veröffentlicht.

http://www.intel.com/content/dam/do...-11-1-processor-power-delivery-guidelines.pdf

Genaue Aussagen im Bezug auf einzelne Geräte kann man aber meist erst nach umfangreichen Reverse-Engineering machen; ob sinnvoll oder nicht halten sich die Hersteller vor allem bei OC-Mainboards und Grafikkarten oft nicht an die Referenzimplementierung der Stromversorgung sondern entwickeln eigene Lösungen die ihrer Meinung nach eine stabilere Spannungsversorgung bei sehr hohen Strömen gewährleisten können.

_______

Komplexe ASICs sind oft noch weit komplizierter aufgebaut als Platinen. Digitale Schaltungen kann man noch verstehen und näherungsweise aus den Blockschaltbildern der Hersteller und/oder Programmierguides herleiten wobei ältere CPUs oder GPUs oft besser dokumentiert sind aber wie die Schaltung letztendlich wirklich elektrotechnisch aufgebaut sind ist damit noch lange nicht klar. Auch innerhalb des Chips müssen viele Faktoren beachtet werden die nicht aus der Logischen Schaltung an sich hervorgehen wie etwa maximale Stromdichten und Leistungsdichten, gegenseitige EM-Beeinflussung von Leiterbahnen usw. Informationen darüber werden praktisch nie veröffentlicht abgesehen von Die-Shots aus denen man unter Umständen ein wenig über den inneren Aufbau herleiten kann.

Besser hat man es bei ASSPs, insbesondere solchen im Leistungselektronikbereich. Diese sind oft sehr gut dokumentiert, nähere Informationen gibt es vom Hersteller.